# AdvancedTCA® Extensions for Instrumentation and Test

PO Box 1016 • Niwot, CO 80544-1016 • (303) 652-1311 FAX (303) 652-1444

# Technical Backgrounder: The Optical Data Interface Standard October 2, 2017

AXIe Consortium Contact: Bob Helsel Executive Director 303-652-1311 execdir@axiestandard.org

The Optical Data Interface standard, abbreviated as ODI, is a new high-speed interface for instrumentation and embedded systems. ODI breaks speed and distance barriers by relying on optical communication between devices, over a standard pluggable optical fiber. With speeds up to 20 GBytes/s from a single optical port, and speeds up to 80 GBytes/s through port aggregation, ODI is designed to address challenging applications in 5G communications, mil/aero systems, high-speed data acquisition, and communication research.

Since the ODI standard is designed around a standard optical connector, which may be placed anywhere on a device, ODI works equally well with any product format, whether AXIe, PXI, LXI, VPX, or a traditional bench instrument design. It works equally well with instrumentation and embedded systems, such as those found in mil/aero applications. Through the standardized ports, ODI enables high-speed communications between instruments, processors, storage, and embedded devices.

The name Optical Data Interface was carefully chosen. First of all, *Optical* refers to the multi-mode fiber-optic transmission medium that connects from one device to the other. *Data* implies that the standard is aimed at data transmission, not control. Control plane communication is performed over a product's standard interface, such as LAN or PCI Express, to set up the optical connection, which then runs independently until a "stop"

event. *Interface* refers to the concept of a pluggable port, which can be placed anywhere on a product. ODI is high-speed point-to-point optical data connection, not a traditional parallel bus. It is not specific to backplanes at all, though ODI ports may be placed on backplanes.

### **ODI** in Layers

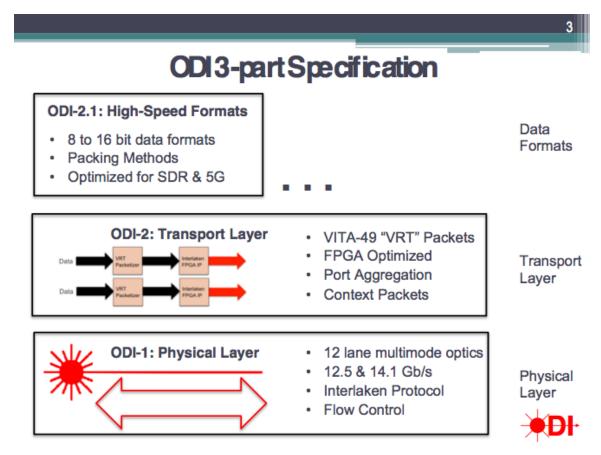

ODI is best understood as a layered specification, as shown in the Figure 1 below.

Figure 1 shows the three specification layers of the ODI family of specifications.

**ODI-1** defines the physical layer- how bits and bytes get from one device to another. It describes a method of transporting packets, without defining what those packets are. It has two layers itself, the optical layer and the protocol layer. The optical layer consists of 12 lanes of multi-mode fiber optics in each direction. A device that transmits data is called a producer, and a device that receives data is a consumer. There are two line rates, 12.5 Gb/s and 14.1 Gb/s. Devices that operate at the higher speed must operate at the lower speed as well, enabling upward compatibility. Multiply 12 lanes by 14.1 Gb/s, and the ODI port is capable of over 160 Gb/s or 20 GBytes/s in each direction. There is no

requirement that data samples be packed in a byte format, and can be any number of bits in length. A device may transmit-only, receive-only, or both. Often, digitizers are uni-directional, while signal generators such as AWGs (arbitrary waveform generators) are bi-directional. Signal generators use flow control in the reverse direction to pace the incoming data to their precise speed, managing the data input buffer.

The protocol layer is defined by the Interlaken standard, a chip-to-chip interconnect standard common in data centers, conceived by Cortina Systems and Cisco Systems. Interlaken is supported by the major FPGA suppliers, and is managed by the Interlaken Alliance. It delivers packets of data over any number of SerDes (serializer/deserializer) lanes, at any speed. The packets are not defined by Interlaken, only their boundaries as a block transfer.

Interlaken manages the health and alignment of the 12 ODI lanes without interrupting data transfer. It also allows flow control from a consumer to modulate the average speed from the producer, using the reverse direction link. This may be used by an AWG to control the data delivery from a storage device.

**ODI-2** defines the ODI transport layer. Here, the packets transported by Interlaken are defined. ODI deploys a standard packet definition, leveraged from the VITA 49 family of standards.

Packets play a critical role in ODI. They envelope the data payload, which contains single channel or multi-channel sample data. Consecutive packets are sent to stream data. Data is stored as packets. Packets enable error recovery from an outage, such as could be caused by an electrostatic discharge. Packets allow port aggregation, the combining of ports to achieve proportionally higher data rates.

ODI has adopted the VITA 49 family of standards for packet definition. <u>VITA</u> is a standards organization well known for its VME and VPX standards, common in many mil/aero embedded applications. VITA 49.0 is titled as the VITA Radio Transport specification, and is often abbreviated as VRT. VRT defines common packet formats and protocols for software defined radios. By adopting a standard that is being deployed by embedded radio systems themselves, ODI expands its applicability from test and measurement to actual operational systems. The ODI Technical Committee (ODI TC) concluded that the VRT specifications have low overhead, are very general in nature, and are applicable well beyond radio communication. Any type of block data may be sent from one device to another.

ODI-2 does two things. First, it defines standard VRT packets for block transfers, allowing a block of data to be sent between manufacturers. Consecutive VRT packets create a "stream" of contiguous data. VRT is very flexible, so the ODI TC chose a subset

optimized for FPGA processing. Embedded in the mandatory packet prologue is a Stream ID, timestamps, and Class ID that identifies the data formats.

Second, ODI-2 uses VRT packets to aggregate ports. For example, a four-port producer sends four nearly simultaneous VRT packets out from each port. The four-port consumer aligns the packets to aggregate the traffic. In this case, a four-port system quadruples the data bandwidth to 640 Gb/s, or 80 GBytes/s.

It should be noted that ODI also supports VRT Context Packets as optional capability. Context packets are used to send meta-data about the specific data stream. This may include the sample rate, reference level, bandwidth, or RF or IF reference frequencies.

#### **ODI-2.1**

For maximum interoperability, ODI-2.1 defines specific data formats and context packets optimized for high-speed data streaming and gate array processing. ODI-2.1 mandates 8-bit and 16-bit real and complex data transfers, and specific packing of the data into the packet's data payload.

It optionally allows link-efficient packing of 9-bit to 15-bit real and complex data for maximum data throughput. Link-efficient packing packs data on the sample length boundaries (e.g. 10-bit boundaries for 10-bit data) instead of 32-bit word boundaries used for 8-bit and 16-bit data.

- ODI-2.1 packs multi-channel data in a round-robin manner into the data payload. The data format and the number of channels is specified in the Class ID field of the VRT packet prologue. Data is stored with the same identifiers as well. This allows both streamed data and stored data to be interpreted and processed between vendors.

- ODI-2.1 also supports events on a per-sample basis. This allows indicators, such as markers, triggers, or overload detection to be embedded with each sample. This is a key feature of many digitizers and AWGs, and the location and number of event bits are also determined by the Class ID.

- ODI-2.1 defines a standardized Context Packet optimized for FPGA processing. The combination of Reference Level and Sample Rate define the amplitude and speed of the digitized signal. It is equally applicable to oscilloscopes and AWGs as it is to RF digitizers and signal generators.

- ODI-2.1 is a high-speed equivalent of VITA 49A. VITA 49A chose a subset of VITA 49.0 protocols optimized for 32-bit and 64-bit general-purpose processors connected through IP networks. ODI-2.1 focuses on 8-bit to 16-bit real and complex data, easily manipulated by FPGAs. However, for the ODI-2.1 standard, the ODI TC chose Class ID

values to closely mimic VITA 49A values. This essentially allows any VITA 49A data format definition to be transported by ODI.

# **ODI Implementation**

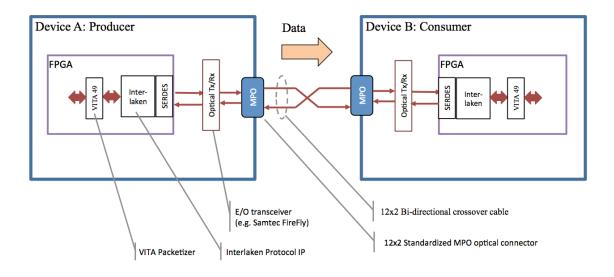

Another way to view ODI is the implementation shown in Figure 2 below.

Figure 2 shows the basic components of an ODI link as data is sent from the producer to the consumer.

Figure 2 puts everything together. It is easiest to analyze the figure from the middle out, starting with the optical link.

Each device has a MPO (Multi-fiber Push On) connector, which houses two rows of 12 fibers each. The top row is for transmit functions, and the bottom half is for receive functions. The standard ODI cable is a 24-fiber crossover cable, which automatically connects transmitters to receivers. Uni-directional devices connect their internal fibers to either the optical transmitters or receivers, depending which type of device they are. Bi-directional devices connect to both. Samtec Firefly optical engines meet the ODI specifications, but so do any optics that meet IEEE 802.3ba optical levels and the specified line rates.

The optical E/Os and O/Es (electrical-to-optical converters and optical-to-electrical converters) are then connected to the SerDes lines of the respective FPGAs. The Interlaken IP manages the 12 SerDes in each direction, and sends and receives packet data. The reverse path may be used for flow control. Interlaken IP is available from the

major FPGA vendors, such as Intel Corporation and Xilinx. Contact information for all the component vendors may be found on the <u>ODI Specifications</u> page.

VITA 49 functionality, specified in ODI-2 and ODI-2.1, is chosen and implemented by the device manufacturer. For an instrument, this is typically chosen to match the resolution, number of channels, and data rate of the device. Not all devices need significant packet comprehension to perform their operations. Storage devices, for example, can store or source data without knowledge of the meaning of the data.

### Future

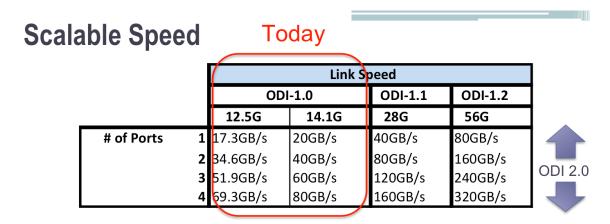

As technologies change, standards must adapt. It is the intent of the ODI standard to follow the speed curves of FPGAs and optical devices. The ODI Technical Committee has examined future optical trends and published the speed roadmap below.

Figure 3 shows today's speeds, defined by the ODI-1 standard. As optical speeds increase, ODI will follow the speed curves.

Figure 3 shows the data speeds available from today's ODI specification. ODI-1 defines the per-port speed, while ODI-2 uses port aggregation to multiply the ODI-1 speed by the number of aggregated ports.

Two speeds were chosen in ODI-1. 12.5 Gb/s FPGAs and their bundled Interlaken solutions offer an economical alternative if per port rates don't exceed 17.3 GBytes/s. For instruments requiring the full 20 GBytes/s throughput, 14.1 GBytes/s is available. In general, higher speed devices must support the slower rates as well, delivering backwards compatibility. There are some exceptions to this rule, such as in the case that the aggregate bandwidth required exceeds that possible with the slower rates. This same

compatibility requirement will be used going forward as optical devices double their speed to 28 Gb/s, supporting the 12.5 Gb/s and 14.1 Gb/s line rates.

All future rates and implementations should be considered somewhat speculative at this point. Nevertheless, the ODI TC has published the above figure as a directional document. At least through 28 Gb/s, the port definition of the two 12-row MPO connector and the optical cable remain the same, though interconnect distances will shrink somewhat from the current 100-meter cable length limit. Twelve lanes are the most cost-effective solution today, and a 12-lane port is easy to implement even if the industry transitions to 4–lane and 8-lane optics in the future. Interlaken IP supports 12-lane and 24-lane transmission, allowing another option for increased pre-port speed.

### **ODI Standard Management**

The ODI specifications are managed by the AXIe Consortium. Any organization or vendor may develop and offer ODI-compatible devices without restriction. There are no license fees, and membership in the AXIe Consortium is not required.

Any organization or vendor may participate in the ODI Technical Committee by joining the AXIe Consortium.

The ODI Technical Committee (ODI TC) is a subset of the AXIe Technical Committee and manages the details of the specifications, subject to final approval by the AXIe Board of Directors. The ODI TC determines the content of the specifications, and when revisions are updated. The current specifications are in slide format, marked as Preliminary. The ODI TC plans to organize interoperability workshops to test key functionality between vendors, and to fine-tune the specifications where needed. Once interoperability testing is complete, the preliminary specifications will transition to formal specifications.

The ODI Technical Committee has identified two additional areas for standardization, common APIs (application programming interface) and test modes. The two documents are known as ODI-A and ODI-T respectively. The ODI-A standard establishes recommendations for implementing the programming interface for the ODI family of specifications. The ODI-T standard recommends test modes to verify and troubleshoot the optical link.

#### More Information

More information may be found on the <u>AXIe Consortium website</u>.

###